# Programming a toy computer from scratch

A practical introduction to computer systems

**Eric Bruneton**

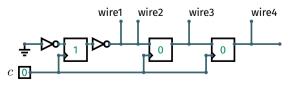

# Programming a toy computer from scratch

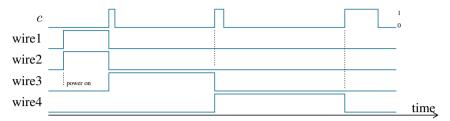

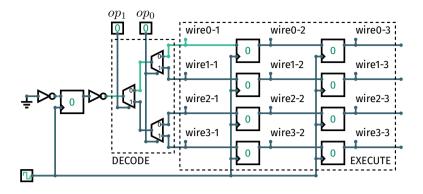

A practical introduction to computer systems

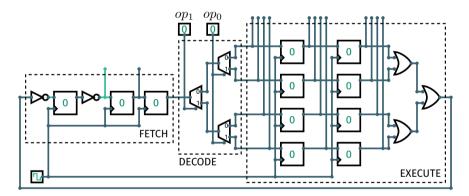

**Eric Bruneton**

© 2024 Eric Bruneton

### Version

This book was built from commit 1fc6f0aca63fba948c923e9c8a35ccc3452296da on August 19, 2024 in the source code repository. The latest version can be downloaded at https://ebruneton.github.io/toypc/.

### Source code

The source code of this book, in LATEX and Rust, is available at https://github.com/ebruneton/toypc. The programs it describes are also available separately, at https://ebruneton.github.io/toypc/.

#### Feedback

Please report errors or potential improvements at https://github.com/ebruneton/toypc/issues.

# Contents

| Introduction                                     |

|--------------------------------------------------|

| PART 1 A Toy Microprocessor 1                    |

| Introduction                                     |

| CHAPTER 1 Binary Numbers                         |

| <b>1.1</b> Binary numbers                        |

| <b>1.2</b> Arithmetic operations                 |

| <b>1.3</b> Logical operations                    |

| <b>1.4</b> Hexadecimal numbers                   |

| CHAPTER 2 Logic Gates and Arithmetic Circuits 13 |

| <b>2.1</b> Transistors                           |

| <b>2.2</b> Logic gates                           |

| <b>2.3</b> Multiplexers and demultiplexers       |

| <b>2.4</b> Arithmetic circuits                   |

| CHAPTER 3 Register and Memory Circuits 23        |

| <b>3.1</b> Memory cells                          |

| <b>3.2</b> Memory circuits                       |

| <b>3.3</b> Bus                                   |

| <b>3.4</b> Example                               |

| CHAPTER 4 Control Circuits                       |

| <b>4.1</b> Instructions                          |

| <b>4.2</b> A toy instruction set                 |

| <b>4.3</b> Control circuits                      |

| <b>4.4</b> A toy control unit                    |

| <b>CHAPTER 5 A Toy Microprocessor</b>            |

| <b>5.1</b> Implementation                        |

| <b>5.2</b> Example programs                      |

| <b>Conclusion</b>                                |

| PART   | <b>2 A Basic Input Output System</b> 53                     |

|--------|-------------------------------------------------------------|

| Introd | <b>action</b>                                               |

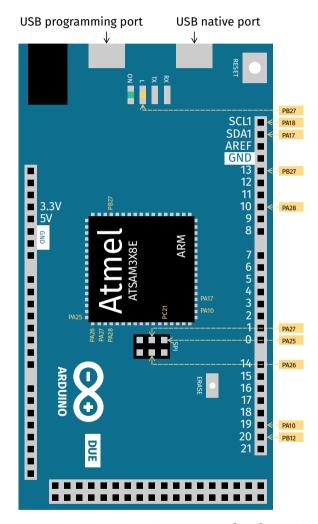

| СНАРТ  | ER 6 First Steps with the Arduino Due 59                    |

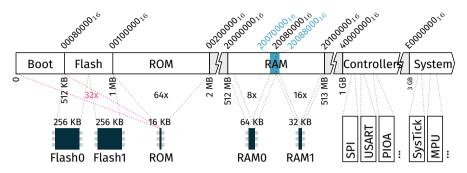

| -      | Overview of the Arduino Due                                 |

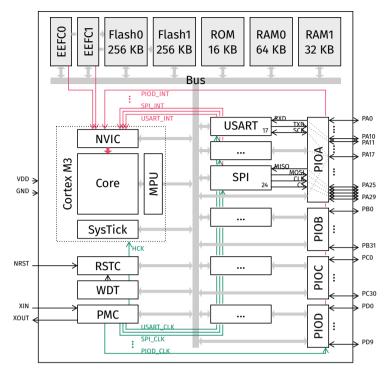

|        | Overview of the Atmel SAM3X8E                               |

|        | Memory bus                                                  |

|        | Boot assistant                                              |

| 6.5    | Flash controller                                            |

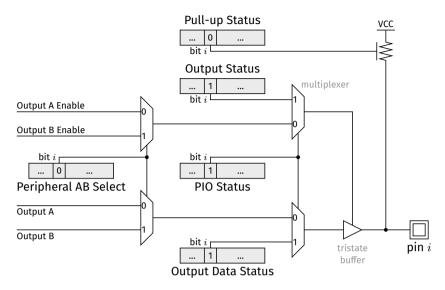

| 6.6    | Parallel Input Output controller                            |

| СНАРТ  | ER 7 First Steps with the Cortex M3 75                      |

| 7.1    | Overview of the Cortex M3                                   |

| 7.2    | Registers                                                   |

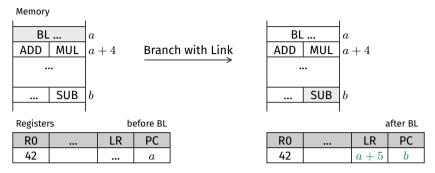

|        | Instruction set                                             |

|        | Vector Table                                                |

|        | First program                                               |

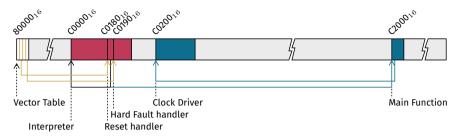

| CHAPT  | ER 8 Virtual Machine 93                                     |

|        | Overview                                                    |

|        | Bytecode instructions                                       |

|        | Interpreter                                                 |

|        | Example program                                             |

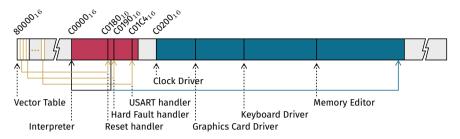

| CHAPT  | <b>ER 9 Clock Driver</b>                                    |

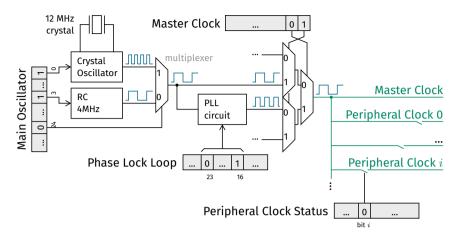

| 9.1    | Power Management Controller                                 |

|        | System Timer                                                |

|        | Watchdog Timer                                              |

|        | Clock initializer                                           |

|        | Delay function                                              |

|        | Basic input output system foundations                       |

|        | Experiments                                                 |

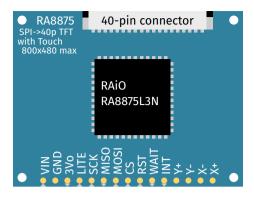

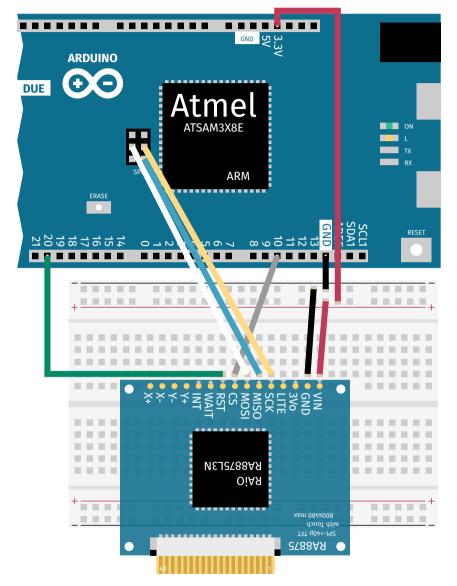

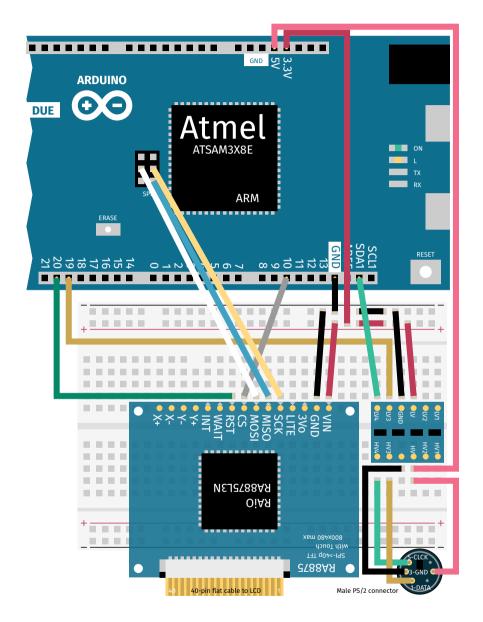

|        | <b>ER 10</b> Graphics Card Driver                           |

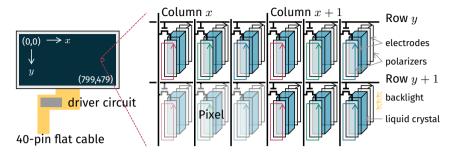

|        | Liquid Crystal Display                                      |

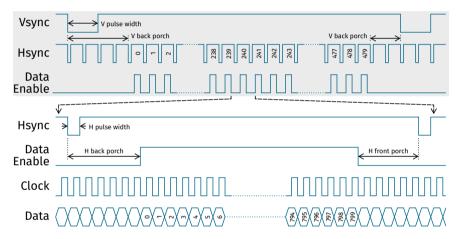

|        | Graphics card                                               |

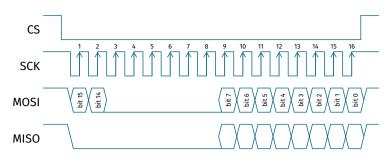

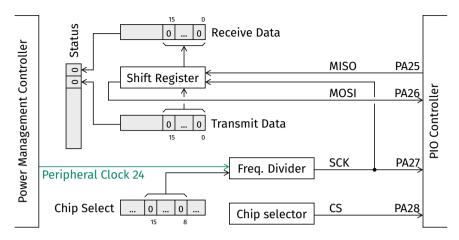

|        | Serial Peripheral Interface component                       |

|        | Graphics card driver                                        |

|        | Experiments                                                 |

| CHAPT  |                                                             |

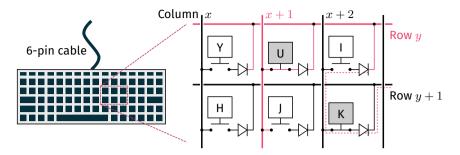

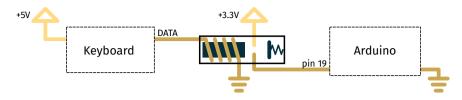

|        | Keyboard                                                    |

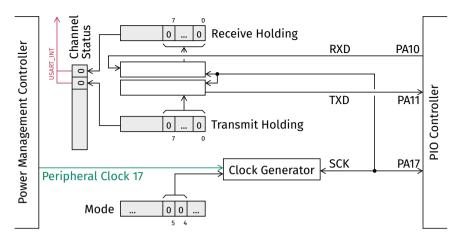

|        | Universal Synchronous Asynchronous Receiver Transmitter 145 |

|        | Nested Vector Interrupt Controller                          |

| 11.4   | Keyboard driver                                             |

| 11.5   | Experiments                |

|--------|----------------------------|

| CHAPT  | ER 12 Memory Editor        |

| 12.1   | User interface             |

| 12.2   | State variables            |

| 12.3   | Drawing functions          |

|        | Editing functions          |

|        | Main function              |

|        | Experiments                |

| Conclu | <b>sion</b>                |

| PART   | <b>3 A Toy Compiler</b> 17 |

| Introd | uction                     |

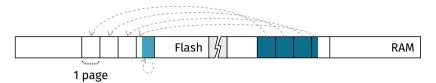

|        | ER 13 Flash Memory Driver  |

|        | Overview                   |

|        | Implementation             |

|        | Storage                    |

|        | ER 14 Text Editor          |

|        |                            |

|        | User interface             |

|        | Implementation             |

|        | Experiments                |

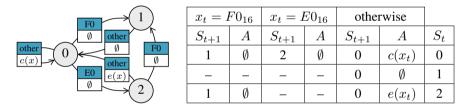

|        | ER 15 Opcodes Compiler     |

|        |                            |

|        | Requirements               |

|        | Implementation             |

|        | Command editor             |

|        | ER 16 Labels Compiler      |

|        | Requirements               |

|        | Algorithms                 |

|        | Implementation             |

|        | Compilation and tests      |

| CHAPT  |                            |

|        | Requirements               |

|        | Algorithms                 |

|        | Implementation         264 |

|        | Compilation and tests      |

| CHAPT  | ER 18 Statements Compiler    |

|--------|------------------------------|

| 18.1   | Requirements                 |

| 18.2   | Algorithms                   |

| 18.3   | Implementation               |

| 18.4   | Compilation and tests        |

| CHAPT  | ER 19 Types Compiler         |

| 19.1   | Requirements                 |

| 19.2   | Algorithms                   |

| 19.3   | Implementation               |

| 19.4   | Compilation and tests        |

| CHAPT  | <b>ER 20</b> Native Compiler |

| 20.1   | Requirements                 |

| 20.2   | Algorithms                   |

| 20.3   | Implementation               |

| 20.4   | Compilation and tests        |

| Conclu | <b>sion</b>                  |

| PART 4 A Toy Operating System              | <b>.</b> . | •• | ••  | • | •• | • | •• | • 375 |

|--------------------------------------------|------------|----|-----|---|----|---|----|-------|

| Introduction                               |            |    |     |   |    |   |    |       |

| CHAPTER 21 File System                     | • • •      | •• | • • | • | •• | • | •• | • 379 |

| <b>21.1</b> Requirements                   |            |    |     |   |    |   |    |       |

| <b>21.2</b> Data structures                |            |    |     |   |    |   |    |       |

| <b>21.3</b> Implementation                 |            |    |     |   |    |   |    |       |

| <b>21.4</b> Compilation and tests          |            |    |     |   |    |   |    |       |

| CHAPTER 22 Boot Loader and Drivers         | 5          | •• | • • | • | •• | • | •• | • 399 |

| <b>22.1</b> Boot loader                    |            |    |     |   |    |   |    | . 399 |

| <b>22.2</b> Compilation and storage        |            |    |     |   |    |   |    | . 403 |

| <b>22.3</b> Drivers                        |            |    |     |   |    |   |    | . 405 |

| <b>22.4</b> Compilation and test           |            |    |     |   |    |   |    | . 414 |

| CHAPTER 23 Processes and System C          | alls       | •• | ••  | • | •• | • | •• | • 417 |

| <b>23.1</b> Requirements                   |            |    |     |   |    |   |    | . 417 |

| <b>23.2</b> Design                         |            |    |     |   |    |   |    | . 418 |

| <b>23.3</b> Data structures and algorithms |            |    |     |   |    |   |    | . 422 |

| <b>23.4</b> Implementation                 |            |    |     |   |    |   |    | . 426 |

| <b>23.5</b> Compilation and tests          |            |    |     |   |    |   |    | . 434 |

| CHAPT  | ER 24 Streams                              |

|--------|--------------------------------------------|

| 24.1   | Requirements                               |

| 24.2   | Design                                     |

|        | Data structures and algorithms             |

|        | Implementation                             |

|        | Compilation and tests                      |

| CHAPT  | ER 25 Shell, Text Editor, and Compiler 455 |

| 25.1   | Shell                                      |

| 25.2   | Text editor                                |

|        | Compiler                                   |

| 25.4   | Self hosting                               |

| CHAPT  | ER 26 Memory Protection                    |

| 26.1   | Memory Protection Unit                     |

| 26.2   | Algorithm                                  |

|        | Implementation                             |

|        | Compilation and tests                      |

| CHAPT  | ER 27 Utilities                            |

| 27.1   | Split                                      |

| 27.2   | Reboot                                     |

|        | Delete                                     |

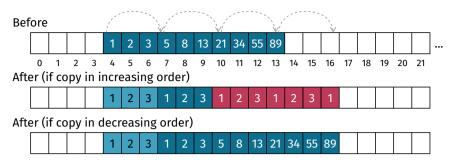

|        | Copy                                       |

|        | List                                       |

|        | Stat                                       |

|        | Compiler improvements                      |

|        | Shell improvements </th                    |

|        | *                                          |

|        | <b>ER 28 Snake Game</b>                    |

|        | Requirements                               |

|        | Data structures                            |

|        | Implementation                             |

|        | Compilation and play                       |

| Conclu | <b>sion</b>                                |

| <b>References</b> . |                        |

|---------------------|------------------------|

| <b>APPENDIX A</b>   | Bill of Materials      |

| APPENDIX B          | <b>ASCII codes</b>     |

| APPENDIX C          | IBM PC Set 2 scancodes |

| APPENDIX D          | Compiler error codes   |

| APPEN      | DIX E     | Boot   | Ass | sis | ta | nt | S | cri | pt | S | • | • | • | • | • | • | • | • • |   | • | • | • | • | • 529 |

|------------|-----------|--------|-----|-----|----|----|---|-----|----|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|-------|

| E.1        | boot_hel  | per.py |     |     |    | •  |   |     | •  |   |   |   |   |   |   |   |   |     |   |   |   |   |   | . 529 |

| <b>E.2</b> | flash_hel | per.py |     |     |    | •  |   |     | •  |   | • | • | • |   | • | • | • | •   | • | • | • |   |   | . 530 |

# Introduction

Billions of people are using computers or smartphones, which are computers before being phones. One doesn't need to understand how computers work to use them, but if you want to know, this book might help you.

Popular science books about this topic intentionally leave out many details. On the other hand, textbooks emphasize theoretical aspects and focus on a narrow topic. This book is different. Its goal is to introduce how computer hardware and common programming languages and operating systems work, via a practical example which can be understood down to the smallest detail.

For this it proposes you to assemble and program your own toy computer. And to make sure not to omit any details, it explains how you can do this from scratch, without using any existing programming tool. It is organized in four parts:

- the first part briefly presents the main basic ideas used to design microprocessors, which are the core component of a computer. This is necessary to understand the main concepts used in the next parts. It ends with the presentation of a virtual, toy microprocessor, which can be simulated online, and of a few programs using it.

- the second part explains how the components of your toy computer work, how they can be programmed, and how to assemble them. Based on this, it then describes how to build a basic system allowing programs to use the computer's keyboard and screen. Finally, it presents how an initial program can read and execute other programs, based on this input and output system.

- the third part explains how a computer can be programmed in a language which can be "easily" understood by humans, unlike the 0s and 1s used by its microprocessor. For this it describes how to progressively build a toy language, and a program which can translate it into 0s and 1s that the microprocessor can execute. In order to give you an idea of what common programming languages look like, this toy language is an extremely simplified version of real and popular ones.

- the fourth part explains how users can easily store files and launch applications on their computer, thanks to a (set of) program(s) called an operating system. For this it describes how to progressively build a toy operating system for your toy computer. For the same reason as above, this system is an extremely simplified version of real, frequently used ones.

### **Target audience**

This book is designed for people looking for a practical and fully detailed example introducing how microprocessors, programming languages and operating systems work. It does not explain the theories and principles behind this. If you want to learn them, you should read computer science textbooks instead (some references are provided at the end of each part). Conversely, if you only want to understand the general ideas, it is better to read popular science books instead.

#### How to read this book

You can read this book without actually assembling or programming a toy computer, just to understand how this could be done. In this case you can skip the tutorial-like sections, which describe concrete steps to follow (plug this wire here, type this on the keyboard, press this button, etc). This is the case, in particular, of the "Experiments" and "Compilation and tests" sections.

Alternatively, you can read this book while following the instructions on an emulator. In this case you do not need to assemble a toy computer, nor to buy the necessary components for this (described in Appendix A). Instead, simply use the emulator provided at https://ebruneton.github.io/toypc/emulator.html. For this you need a desktop or laptop computer (tablets and smartphones are not really usable for this task).

Finally, you can buy the components, assemble them, and follow the instructions for real. This is more costly but probably more fun than the previous methods. This method also requires a desktop or laptop computer, with a USB port and capable of running python3. You can also use all three methods: start with the first one, then re-read the book with the second method and optionally with the third, if you feel that you need to (typing a program is slower than reading it – this can trigger some questions, and finding the answers yourself can give you a better understanding).

Note also that, if you are stuck or simply want to skip some steps, you can follow the instructions of any chapter without doing those of the previous ones (once the computer is physically assembled, if you choose this method). Hence, for instance, you can skip the instructions of part 2, do those of part 3 on the emulator, and those of part 4 for real. You can also already have a look at the final programs and operating system obtained at the end of this book, on the emulator, by opening the following link: https://ebruneton.github.io/toypc/emulator.html?script=backups/final.txt. See the companion website of this book for more details (https://ebruneton.github.io/toypc/).

# Introduction

Before programming a toy computer from scratch it is useful to have some basic ideas about how computers work. For this, one method is to build a toy computer from scratch. It is possible to build one for real from individual electromagnetic relays [5] or transistors [18]. But this requires a lot of time and space, and a significant budget. Moreover, the resulting computer would be too small to run or even store the toy programs of this book. For this reason, this part presents how a toy computer *could* be built, but does not give all the details necessary to physically build one. It is organized as follows:

- Chapter 1 briefly presents binary numbers, which are the basis of how computers work, and how to compute with them.

- Chapter 2 explains how an electric circuit can compute additions and subtractions of binary numbers.

- Chapter 3 shows how loops in circuits can be used to memorize numbers, and in particular the (intermediate) results obtained with the above arithmetic circuits.

- Chapter 4 shows how a circuit can control another, in order to make it perform a series of computations, specified by a *program*.

- Chapter 5 puts everything together to obtain a toy microprocessor, and shows how it can be programmed with a few examples.

**Note** Most of the circuits presented in this part are also available on CircuitVerse (https://circuitverse.org/), an online digital circuit simulator. Thanks to it you can interact with the circuits presented in this part, which helps getting a better and more practical understanding of how they work. See the companion website of this book for more details (https://ebruneton.github.io/toypc/).

CHAPTER

# Binary Numbers

As its name implies, a computer performs computations, on numbers. A number is an abstract concept which can be represented in many different concrete ways. For example, the number of days in a week can be represented with "seven", "7", "VII", etc. Some representation methods, also called numeral systems, are more practical than others to perform computations. For instance, doing additions and multiplications is easier in the arabic numeral system than in the roman one. In fact they are even easier to do in the so called *binary numeral system*. Computers use it for this reason. In order to understand how they work it is thus necessary to know first what binary numbers are, and how to compute with them. This is the goal of this chapter.

### 1.1 Binary numbers

An arabic number such as 237 represents 2 times 100, plus 3 times 10, plus 7 times 1. In mathematical notation this gives

$$237 = 2 * 100 + 3 * 10 + 7 * 1 = 2 * 10^{2} + 3 * 10^{1} + 7 * 10^{0}$$

where  $x^n$  denotes 1 if n = 0, or x \* x \* ... x (*n* times) otherwise. In other words, an arabic number is a sequence of digits between 0 and 9, where the  $i^{th}$  digit from the right (counting from 0) represents a quantity of  $10^i$ .

A binary number is similar but uses two digits instead of ten, namely 0 and 1, called *bits*. It is thus a sequence of bits, where the  $i^{th}$  bit from the right (counting from 0) represents a quantity of  $2^i$ . For example

$$101_2 = 1 * 2^2 + 0 * 2^1 + 1 * 2^0 = 1 * 4 + 0 * 2 + 1 * 1 = 5$$

where the subscript 2 indicates a binary number (to avoid confusions with arabic numbers;  $101_2 = 5 \neq 101$  = "one hundred one"). Another example is

$$11101101_{2} = 1 * 2^{7} + 1 * 2^{6} + 1 * 2^{5} + 0 * 2^{4} + 1 * 2^{3} + 1 * 2^{2} + 0 * 2^{1} + 1 * 2^{0}$$

= 1 \* 128 + 1 \* 64 + 1 \* 32 + 0 \* 16 + 1 \* 8 + 1 \* 4 + 0 \* 2 + 1 \* 1

= 237

The leftmost bit of a binary number is called its *most significant* bit. Conversely, the rightmost bit is called the *least significant*. The  $i^{th}$  bit from the right (counting from 0), is called bit number *i*, or simply bit *i*.

### **CHAPTER 1** Binary Numbers

| n  | $2^n$ | $2^n$                | $2^{n} - 1$ | $2^n - 1$             |

|----|-------|----------------------|-------------|-----------------------|

| 0  | 1     | $1_{2}$              | 0           | 0                     |

| 1  | 2     | $10_{2}$             | 1           | 1                     |

| 2  | 4     | $100_{2}$            | 3           | $11_2$                |

| 3  | 8     | $1000_{2}$           | 7           | $111_{2}$             |

| 4  | 16    | $10000_2$            | 15          | $1111_2$              |

| 5  | 32    | $100000_2$           | 31          | $11111_2$             |

| 6  | 64    | $1000000_2$          | 63          | $111111_2$            |

| 7  | 128   | $1000000_2$          | 127         | $1111111_2$           |

| 8  | 256   | $10000000_2$         | 255         | $11111111_2$          |

| 16 | 65536 | $1000000000000000_2$ | 65535       | $11111111111111111_2$ |

TABLE 1.1

Some frequently used powers of 2, in arabic and binary notation.

Some numbers have a very simple binary representation and are frequently used. For instance,  $2^n$  is a one followed by n zeros in binary, like  $10^n$  in arabic notation. Another example is  $2^n - 1$ , which is simply n ones (like  $10^n - 1$  is n nines in arabic). Table 1.1 gives some examples of these numbers.

### **1.2 Arithmetic operations**

### 1.2.1 Addition

Adding two binary numbers can be done as with arabic numbers. Namely one column at a time, from right to left. For instance, adding  $1101010_2$  and  $101110_2$  can be done as follows:

| $\begin{smallmatrix}1&1&1&1&1\\&1&1&0&1&0&1&0\end{smallmatrix}$ | $1\overset{1}{0}6$ |

|-----------------------------------------------------------------|--------------------|

| + 101110                                                        | + 46               |

| 10011000                                                        | 152                |

Starting from the right, we add 0 and 0, which gives 0. We then add 1 and 1, which gives  $2 = 10_2$ . Since this is more than one bit, we put the least significant one, here 0, in the current column, and we *carry* the most significant one, here 1, in the column on the left (shown in red). This is similar to the addition of the equivalent arabic numbers, shown on the right, where 6 + 6 gives 12, leading to a carry of 1.

We continue by adding 0 and 1, plus the carry from the previous column, which gives 2 again. In the next step we add 1 and 1, plus the carry from the previous column, which gives  $3 = 11_2$ . We thus put 1 at the bottom of this column, and carry 1 in the next one. And so on for the remaining columns.

Although the overall process is the same for binary and arabic numbers, adding binary numbers is much easier, as stated above. Indeed, there are only 2 \* 2 = 4

### 1.2 Arithmetic operations

| result bit: | a | b | a+b |  |

|-------------|---|---|-----|--|

|             | 0 | 0 | 0   |  |

|             | 0 | 1 | 1   |  |

|             | 1 | 0 | 1   |  |

|             | 1 | 1 | 0   |  |

| carry bit: | а | b | a+b |

|------------|---|---|-----|

|            | 0 | 0 | 0   |

|            | 0 | 1 | 0   |

|            | 1 | 0 | 0   |

|            | 1 | 1 | 1   |

TABLE 1.2 The binary addition tables.

| result bit: | а | b | a-b | carry bit: |

|-------------|---|---|-----|------------|

|             | 0 | 0 | 0   |            |

|             | 0 | 1 | 1   |            |

|             | 1 | 0 | 1   |            |

|             | 1 | 1 | 0   |            |

| : | а | b | a-b |

|---|---|---|-----|

|   | 0 | 0 | 0   |

|   | 0 | 1 | 1   |

|   | 1 | 0 | 0   |

|   | 1 | 1 | 0   |

TABLE 1.3 The binary subtraction tables.

possible cases when adding two bits, but 10 \* 10 = 100 cases when adding two decimal digits. These four cases are summarized in Table 1.2.

### 1.2.2 Subtraction

Similarly, subtracting two binary numbers can be done as with a abic numbers. For instance, subtracting  $101110_2$  from  $1101010_2$  can be done as follows:

| 1101010 | 106  |

|---------|------|

| -101110 | -146 |

| 0111100 |      |

Starting from the right, we subtract 0 from 0, and then 1 from 1, which gives 0 in both cases. In the next step, since we cannot subtract 1 from 0, we subtract it from  $10_2 = 2$  instead, which gives 1. We thus put a 1 in the current column, and a carry of 1 in the subtrahend on the left column (shown in red). This is similar to the subtraction of the equivalent arabic numbers, shown on the right, where 0 - 4 is replaced with 10 - 4, yielding the result 6 and the carry 1.

We continue by subtracting 1, plus the carry from the previous column (*i.e.*, a total of 2), from 1. Since this is not possible we subtract them from  $11_2 = 3$  instead, which gives the result 1 and the carry 1. And so on for the remaining columns.

As with additions, there are only four possible cases when subtracting two bits, which is much simpler than the hundred possible cases for decimal digits. These four cases are summarized in Table 1.3.

### **CHAPTER 1** Binary Numbers

### 1.2.3 Multiplication

Multiplying two binary numbers can also be done as with arabic numbers. Namely by multiplying the first by each bit / digit of the second. And by adding the results, each shifted by one bit / digit to the left from the previous one. For instance, multiplying  $1101010_2$  by  $101110_2$  can be done as follows:

|      | 1101010   |                   |

|------|-----------|-------------------|

| *    | 101110    |                   |

|      | 0000000   | 106               |

|      | 1101010   | * 46              |

|      | 1101010   | 636               |

| 1    | 101010    | 424               |

| 0.0  | 00000     | $\overline{4876}$ |

| 110  | 01010     |                   |

| 1001 | 100001100 |                   |

Here again, although the process is the same, multiplying binary numbers is much easier than arabic numbers. Indeed, multiplying the first number by each bit of the second boils down to multiplications by 0 or 1, which are trivial. By contrast, multiplying an arabic number by a decimal digit requires using a multiplication table with 100 possible cases. It also involves carries.

Some multiplications are even easier to do than with the general method described above. In particular, multiplying x by  $2^n$  can be done by simply shifting x by n bits to the left, *i.e.*, by adding n zeros on the right. For instance,  $1101010_2 = 106$  multiplied by  $2^3 = 8$  is simply  $1101010000_2 = 848$ . This is similar to multiplications by  $10^n$  in arabic notation (for example, 46 times  $10^3 = 1000$  is 46000). Shifting a binary number x by n bits to the left is noted  $x \ll n$ .

The opposite operation, shifting x by n bits to the right, *i.e.*, dropping the n least significant bits, is noted  $x \gg n$ . It corresponds to dividing x by  $2^n$ . For instance, shifting  $1101010_2 = 106$  by 3 bits to the right gives  $1101_2 = 13 = \lfloor 106/2^3 \rfloor^1$ . This is similar to dropping the n least significant digits of an arabic number, which divide it by  $10^n$  (for example, 4876 shifted to the right by 2 digits is  $48 = \lfloor 4876/100 \rfloor$ ). Dividing arbitrary binary numbers can be done as with arabic numbers, but is not presented here.

### 1.2.4 Conversions

Computers do all their computations with binary numbers because, as shown above, this is much easier to do than with arabic numbers. However, humans prefer to specify inputs with arabic numbers, and to get results in arabic too. This requires converting arabic numbers to binary ones, and vice versa.

The |x| notation designates the integer part of x. For instance, 106/8 = 13.25 and |13.25| = 13.

#### 1.3 Logical operations

One method to convert an arabic number to binary is to convert each digit from left to right, and to multiply the result by 10 before adding the next digit. For instance, to convert 46 to binary, we start by converting 4, which gives  $100_2$ . We multiply this by 10 = 8 + 2, which can be done by shifting  $100_2$  by 3 bits and by 1 bit to the left, and by adding the results:  $100000_2 + 1000_2 = 101000_2$ . Finally we convert 6, which gives  $110_2$  and we add this to the previous result, yielding  $101110_2$ . This method is well suited for computers since it only involves computations on binary numbers (plus a small conversion table for each digit from 0 to 9).

Another method consists in dividing the arabic number by 2 repeatedly. The remainders give the bits of the equivalent binary number, from right to left. For instance, dividing 46 by 2 repeatedly gives 23 (remainder 0), 11 (remainder 1), 5 (remainder 1), 2 (remainder 1), 1 (remainder 0), and 0 (remainder 1). The corresponding binary number is thus  $101110_2$ . Since this method involves divisions on arabic numbers, it is more adapted for humans than for computers.

Similarly, one method to convert a binary number to arabic is to "convert" each bit from left to right, and to multiply the result by 2 before adding the next bit. For instance, converting  $101110_2$  gives successively 1, 1 \* 2 + 0 = 2, 2 \* 2 + 1 = 5, 5 \* 2 + 1 = 11, 11 \* 2 + 1 = 23, and 23 \* 2 + 0 = 46. Since this method involves multiplications of arabic numbers, it is more adapted for humans. But it can also be used on computers, if necessary.

Another method to convert a binary number is to divide it by 10 repeatedly. The remainders, converted to arabic, give the digits of the equivalent arabic number, from right to left. It is well suited for computers since it only involves computations on binary numbers (plus a small conversion table for each binary number from 0 to  $1001_2 = 9$ ).

### 1.3 Logical operations

Binary numbers can also be used to perform *logical operations*, unlike arabic numbers. A logical operation computes whether some *proposition* is true of false, depending on the status of one or more other propositions. A proposition is a statement which is either true or false.

Consider for example a keyboard. A proposition might be "the E key is currently pressed", "the left Shift key is currently released", or "the e letter is currently pressed". They are either true or false, depending on the current state of the keyboard. These propositions, noted KeyPressed(k), KeyReleased(k), and LetterPressed(l), are not completely independent. Some can be computed from the others. For example, we can compute KeyReleased(k) as the opposite of KeyPressed(k). This logical operation is the *negation*, also called *not*, and is noted  $\neg$ :

$$KeyReleased(k) = \neg KeyPressed(k)$$

We can also compute whether the proposition "a Shift key is pressed" is true from the above propositions. Indeed, this is the case if at least one of the two Shift keys is

### **CHAPTER 1** Binary Numbers

| р | $\neg p$ | р | q | $p \wedge q$ | р | q | $p \lor q$ | р | q | $p\oplus q$ |

|---|----------|---|---|--------------|---|---|------------|---|---|-------------|

| 0 | 1        | 0 | 0 | 0            | 0 | 0 | 0          | 0 | 0 | 0           |

| 1 | 0        | 0 | 1 | 0            | 0 | 1 | 1          | 0 | 1 | 1           |

|   |          | 1 | 0 | 0            | 1 | 0 | 1          | 1 | 0 | 1           |

|   |          | 1 | 1 | 1            | 1 | 1 | 1          | 1 | 1 | 0           |

**TABLE 1.4** The truth tables of not ( $\neg$ ), and ( $\land$ ), or ( $\lor$ ), and exclusive or ( $\oplus$ ).

pressed. This logical operation is the *disjunction*, also called *or*, and is noted  $\lor$ :

$ShiftPressed = KeyPressed(LeftShift) \lor KeyPressed(RightShift)$

The keyboard is in "uppercase mode" if a Shift key is currently pressed, or if caps are locked, but not both (a Shift key reverses the effect of CapsLock). This logical operation is the *exclusive disjunction*, also called *exclusive or*, and is noted  $\oplus$ :

$UppercaseMode = ShiftPressed \oplus CapsLocked$

As a last example, we can also compute whether LetterPressed(E) is true from KeyPressed(E) and UppercaseMode. Indeed, this is the case if both are true. This logical operation is the *conjunction*, also called *and*, and is noted  $\land$ :

LetterPressed(E) = KeyPressed(E)  $\land$  UppercaseMode LetterPressed(e) = KeyPressed(E)  $\land \neg$ UppercaseMode

The above logical operations do not depend on the meaning of the propositions, but only on whether they are true or false. And their result is either true or false. For instance,  $\neg$  true is false,  $p \land q$  is true if and only if both p and q are true,  $p \lor q$  is true if at least one of p and q is true, etc. By representing true with 1 and false with 0, they can be seen as operations on individual bits. This gives, for example,  $\neg 1 = 0$ ,  $1 \land 0 = 0$ ,  $1 \land 1 = 1$ , etc. By doing this for all possible cases we get the *truth table* of each operation, represented in Table 1.4. Note that the truth tables of  $\oplus$  and  $\land$  are identical to those giving the result and carry bit of a + b, respectively (see Table 1.2). The result bit of a - b is also equal to  $a \oplus b$ , and the carry bit is  $b \land \neg a$  (see Table 1.3). Hence, it suffice to know how to implement these logical operations with electric circuits, or other technologies, in order to be able to implement arithmetic circuits.

We can then generalize these logical operations from individual bits to whole binary numbers. By definition, a *bitwise* logical operation on two binary numbers is done by applying it on each bit separately, column by column. Thus, for instance:

| 1100          | 1100        | 1100                 |

|---------------|-------------|----------------------|

| $\wedge 1010$ | $\vee 1010$ | $\oplus  1  0  1  0$ |

| 1000          | 1110        | 0110                 |

This can be used to perform several logical operations in parallel (since there is no carry each column can be computed independently of the others, possibly at the same time). For instance, we can represent the current state of a 100 keys keyboard with a 100 bits binary number S, using one bit per key. We can then do the following operations, which are commonly used in many similar contexts:

- to check whether at least one letter key is pressed, we can compute S ∧ L, where L is the binary number whose i<sup>th</sup> bit is 1 if and only if the i<sup>th</sup> key is a letter. If the result is 0 no letter key is pressed, otherwise at least one is pressed.

- if a new set of keys if pressed, we can compute the representation of the new keyboard state with  $S' = S \lor P$ , where P represents the newly pressed keys. For instance, if the  $0^{th}$  and  $3^{rd}$  keys are currently pressed, and if the user presses the  $0^{th}$  and  $2^{nd}$  keys<sup>2</sup>, we get  $S = 1001_2$ ,  $P = 101_2$  and  $S' = 1101_2$ . This correctly represents the fact that the  $0^{th}$ ,  $2^{nd}$ , and  $3^{rd}$  keys are now pressed.

- if a new set of keys if released, we can compute the representation of the new keyboard state with  $S' = S \land \neg R$ , where R represents the newly released keys. For instance, if the  $0^{th}$  and  $3^{rd}$  keys are currently pressed, and if the user releases the third, we get  $S = 1001_2$ ,  $R = 1000_2$  and S' = 1. This correctly represents the fact that only the  $0^{th}$  key remains pressed.

### 1.4 Hexadecimal numbers

Binary numbers are very practical to perform computations, but are not very compact. Arabic numbers are much more compact (a given number has about 3.3 less digits than bits on average), but converting between binary and arabic is not so easy. To solve these issues *hexadecimal* numbers are commonly used.

Hexadecimal numbers are like arabic numbers, but use 16 digits instead of 10. They are called hex digits and are noted 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A (= 10), B (= 11), C (= 12), D (= 13), E (= 14), and F (= 15). An hexadecimal number is thus a sequence of hex digits, where the  $i^{th}$  hex digit from the right (counting from 0) represents a quantity of  $16^i$ . For instance

$$ED_{16} = E_{16} * 16^1 + D_{16} * 16^0 = 14 * 16 + 13 = 237$$

where the subscript 16 indicates an hexadecimal number (to avoid confusions with words or arabic numbers;  $10_{16} = 16 \neq 10$  = "ten").

Each hex digit can be represented with up to 4 bits, and each group of 4 bits can be represented with an hex digit, as shown in Table 1.5. It is thus very easy to convert a binary number to hexadecimal: simply convert each group of 4 bits independently, with Table 1.5. For instance, to convert  $11101101_2$ , we convert  $1110_2$  ( $E_{16}$ ),  $1101_2$ ( $D_{16}$ ), and concatenate the results, yielding  $ED_{16}$ . Conversely, to convert  $ED_{16}$ to binary we simply concatenate the conversions of  $E_{16}$  ( $1110_2$ ) and  $D_{16}$  ( $1101_2$ ), yielding  $11101101_2$ .

<sup>&</sup>lt;sup>2</sup>A pressed key can be "pressed" again due to autorepeat.

### **CHAPTER 1** Binary Numbers

| binary | hex | binary | hex | binary | hex | binary | hex |

|--------|-----|--------|-----|--------|-----|--------|-----|

| 0000   | 0   | 0100   | 4   | 1000   | 8   | 1100   | С   |

| 0001   | 1   | 0101   | 5   | 1001   | 9   | 1101   | D   |

| 0010   | 2   | 0110   | 6   | 1010   | Α   | 1110   | Ε   |

| 0011   | 3   | 0111   | 7   | 1011   | В   | 1111   | F   |

**TABLE 1.5** Conversion between binary and hexadecimal.

Hexadecimal numbers are thus compact (a given number has about 4 times less hex digits and bits) and easy to convert to and from binary, which solves the above issues. On the other hand, doing arithmetic computations with them is harder than with arabic numbers (this involves tables with 16 \* 16 = 256 entries). But this is not necessary since we can convert them to binary, do computations in binary, and convert the result back to hexadecimal.

**CHAPTER**

# 2 Logic Gates and Arithmetic Circuits

As explained in the previous chapter, computing arithmetic operations on binary numbers boils down to the computation of simple logical operations such as conjunctions and exclusive disjunctions. This chapter explains how these operations can be implemented with electric circuits, and then how these circuits can be combined to perform arithmetic operations.

### 2.1 Transistors

In order to implement a logical operation with an electric circuit we first need a way to represent 0 and 1 with some electric states. One possibility is to view a wire connected to the ground as 0, and a wire connected to the power source (*e.g.*, +5V) as 1. To implement a circuit for  $\neg p$ , for instance, we can use an input wire for *p*, and an output wire for the result  $\neg p$ . The circuit in the middle must then connect the output wire to the ground (resp. power source) if the input wire is connected to the power source (resp. ground). A simple switch can do this, provided it is controlled by the input wire, instead of manually. In fact, as illustrated in the next sections, such switches are sufficient to implement any logical operation.

An electric switch itself controlled by electricity connects or disconnects two terminals, hereafter noted *a* and *b*, depending on the voltage or current in a third one, noted *c*. One method to do this is to use a *transistor*. Another method is to use a *relay*. Transistors are much more efficient than relays, and are used virtually everywhere. But relays are simpler to understand and, for this reason, we use them in this chapter to explain how logic gates work.

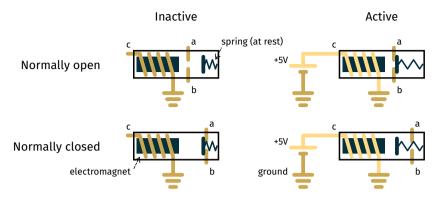

A relay can be built with an electromagnet controlling a metallic connector. There are two types of relays connecting or disconnecting two terminals (see Figure 2.1):

- in a *normally open* relay, the *a* and *b* terminals are disconnected when no current is flowing through the electromagnet. They are connected when the relay is *active*, *i.e.*, when there is a current in the electromagnet.

- in a *normally closed* relay, the *a* and *b* terminals are connected when the relay is *inactive*, *i.e.*, when there is no current in the electromagnet. They are disconnected when it is active.

In the following we represent relays with the symbols illustrated in Figure 2.2. We

### **CHAPTER 2** Logic Gates and Arithmetic Circuits

**FIGURE 2.1** The two types of relays used in this chapter. The electromagnet, when active (right), attracts a metallic piece. This connects the *a* and *b* terminals of a normally open relay (top), and disconnects those of a normally closed one (bottom). When the electromagnet inactive, a spring moves the metallic piece away from it.

**FIGURE 2.2** The symbols and colors used for normally closed (left) and normally open (right) relays, as well as for wires and input (black) and output (blue) terminals connected to the ground, to the power source (up triangle), or to nothing (in red).

draw input terminals connected to the ground (resp. power source) with a 0 (resp. 1) inside a black square. Similarly, we use a 0 (resp. 1) inside a blue square for output terminals connected to the ground (resp. power source). We represent those which are not connected to anything with an X inside a red square. Finally, we draw wires connected to the ground, to the power source, or to nothing in blue, green, and red, respectively (see Figure 2.2).

# 2.2 Logic gates

### 2.2.1 NOT

A *NOT gate* is a circuit implementing the logical not operation. This gate can be built with two relays controlled by the same input<sup>1</sup>. The first, normally closed, connects

<sup>&</sup>lt;sup>1</sup>In practice, with electromagnet relays, 0 can be represented with a terminal connected to the ground or to nothing. Then a single normally closed relay is sufficient to build a NOT gate [5]. In this chapter we do as if it was not the case. This leads to circuits which are much closer to those built with the most common technology, namely Complementary Metal Oxide Semi-conductors (CMOS).

FIGURE 2.3 The two possible states of the NOT gate.

FIGURE 2.4 The four possible states of the AND (top) and NAND (bottom) gates.

the output to the power source by default. The second, normally open, connects the output to the ground when active (see Figure 2.3). Hence, when the input is 0 the first relay connects the output to the power source, *i.e.*, sets it to 1 (while the second does nothing). Conversely, when the input is 1, the first relay has no effect but the second connects the output to the ground, *i.e.*, sets it to 0 (see Figure 2.3).

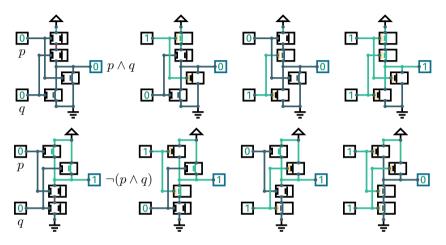

### 2.2.2 AND and NAND

The *AND gate* is a circuit implementing the logical and operation. This circuit must connect the output to the power source when both inputs are 1. This can be done with two normally open relays connected in series. Conversely, this gate must connect the output to the ground when at least one input is 0. This can be done with two normally closed relays connected in parallel (see Figure 2.4).

The *NAND gate* implements the negation of the logical and, *i.e.*, it computes  $\neg(p \land q)$ . It can be obtained by connecting a NOT gate to the output of an AND gate. But a simpler method is to switch the power source and the ground of the AND gate or, equivalently, the upper and lower halves of this circuit<sup>2</sup> (see Figure 2.4).

<sup>&</sup>lt;sup>2</sup>With the CMOS technology "normally closed" (resp. "open") transistors are only used in the upper (resp. lower) half of a gate. Hence a CMOS AND gate is built with a NAND gate followed by a NOT.

#### **CHAPTER 2** Logic Gates and Arithmetic Circuits

FIGURE 2.5 The four possible states of the OR (top) and NOR (bottom) gates.

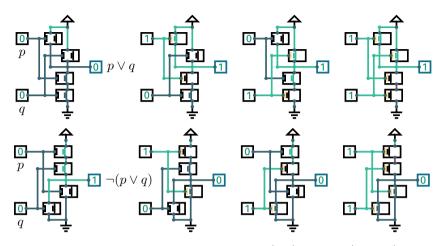

### 2.2.3 OR and NOR

The *OR gate* is a circuit implementing the logical or operation. This gate must connect the output to the power source when at least one input is 1. This can be done with two normally open relays connected in parallel. Conversely, this gate must connect the output to the ground when both inputs are 0. This can be done with two normally closed relays connected in series (see Figure 2.5).

The *NOR gate* implements the negation of the logical or, *i.e.*, it computes  $\neg(p \lor q)$ . As the NAND gate, it can be obtained by switching the upper and lower halves of the OR gate circuit (see Figure 2.5).

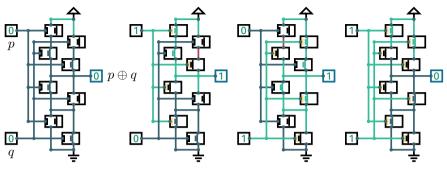

### 2.2.4 XOR

The *XOR gate* implements the exclusive or operation. The result of  $p \oplus q$  is 1 when p is 1 and q is 0, or when p is 0 and q is 1. This gate must thus connect the output to the power source if at least one these two cases happens. This can be done with two sub circuits, one for each case, connected in parallel. Each sub circuit must connect its output to the power source when both inputs have a specific value. This can be done with two relays connected in series: a normally open for p or q, and a normally closed for  $\neg p$  or  $\neg q$ .

Conversely, the result of  $p \oplus q$  is 0 when both "p is 0 or q is 1" and "p is 1 or q is 0" are true. The same reasoning as above leads to two sub circuits connected in series, where each sub circuit uses two relays connected in parallel. This lead to the final circuit shown in Figure 2.6.

In the following, to simplify figures and to make it easier to distinguish each logic gate, we represent them with their American National Standards Institute (ANSI) symbols, shown in Figure 2.7.

### 2.3 Multiplexers and demultiplexers

FIGURE 2.6 The four possible states of the XOR gate.

FIGURE 2.7 The ANSI symbols of the NOT, AND, NAND, OR, NOR and XOR logic gates.

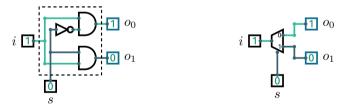

## 2.3 Multiplexers and demultiplexers

Logic gates can be assembled to create more and more complex circuits. A simple example is the *demultiplexer*, shown below, and represented with the symbol on the right:

This circuit copies its input *i* to the  $o_s$  output, *i.e.*, to  $o_0$  if s = 0 or to  $o_1$  if s = 1. It sets the other to 0. It can be viewed as a "railroad switch" for signals. The *multiplexer*, shown below and represented with the symbol on the right, does the opposite:

This circuit sets its output o to the  $i_s$  input, *i.e.*, to  $i_0$  if s = 0, or to  $i_1$  if s = 1.

### CHAPTER 2 Logic Gates and Arithmetic Circuits

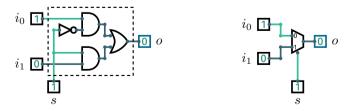

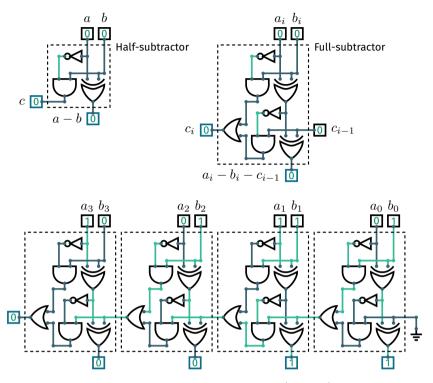

**FIGURE 2.8** A circuit to add two 4-bit numbers (bottom) can be built with 4 full-adder circuits (top right), each made of two half-adders (top left) and an OR gate. Here this circuit computes  $0111_2 + 0011_2 = 1010_2$  (7 + 3 = 10).

# 2.4 Arithmetic circuits

### 2.4.1 Adder

As shown in the previous chapter, the addition of two bits is simply their exclusive disjunction, with a carry equal to their conjunction. In other words, we can add two bits with an XOR gate, plus an AND gate for the carry. The resulting circuit, called a *half-adder*, is illustrated in Figure 2.8.

As explained in Section 1.2.1, adding two binary numbers a and b must be done step by step, from right to left. At each step, one bit  $a_i$  from a must be added to one bit  $b_i$  from b, and to the carry  $c_{i-1}$  from the previous step. In other words, three bits must be added at each step, but the above circuit can only add two. The solution is to connect two copies of it: a first copy adds  $a_i$  and  $b_i$ , and a second adds  $c_{i-1}$  to the result of the first. Each copy produces a new carry, but at most one of these can be 1. Indeed, if  $a_i + b_i$  gives a carry then the second stage necessarily adds  $c_{i-1}$  to 0, which cannot give a carry. Hence the new carry  $c_i$  resulting from  $a_i + b_i + c_{i-1}$  can

### 2.4 Arithmetic circuits

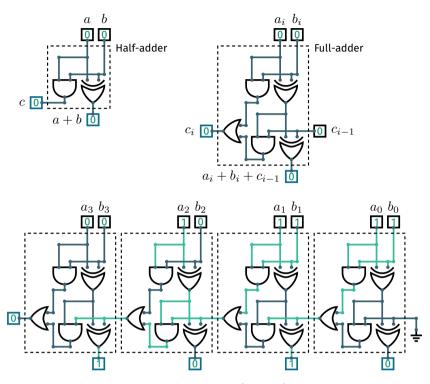

**FIGURE 2.9** A circuit to subtract two 4-bit numbers (bottom) can be built with 4 full-subtractor circuits (top right), each made of two half-subtractors (top left) and an OR gate. Here this circuit computes  $1010_2 - 0111_2 = 0011_2$  (10 - 7 = 3).

be computed with a disjunction of the carries from the two half-adders. This leads to the *full adder* circuit shown in Figure 2.8.

Finally, to add two binary numbers with n bits each, we simply need to connect n full-adder circuits, with the output carry  $c_i$  of step i connected to the input carry  $c_{i-1}$  of step i + 1 (see Figure 2.8).

### 2.4.2 Subtractor

Subtracting two binary numbers can be done with a very similar circuit. As shown in the previous chapter, subtracting a bit *b* from *a* gives their exclusive disjunction (as their addition), plus a carry equal to the conjunction of  $\neg a$  and *b* (versus of *a* and *b* for an addition). In other words, a circuit to subtract *b* from *a* can be obtained by adding a NOT gate in a half-adder circuit. The result, called a *half-subtractor*, is illustrated in Figure 2.9.

Subtracting two binary numbers a and b must be done step by step, from right to left. At each step, one bit  $b_i$  from b, and the carry  $c_{i-1}$  from the previous step, must

#### **CHAPTER 2** Logic Gates and Arithmetic Circuits

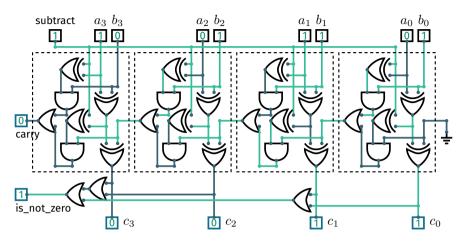

**FIGURE 2.10** A simple Arithmetic Unit which can perform additions, subtractions, and comparisons of 4-bit numbers.

be subtracted from a bit  $a_i$  from a. In other words, three bits must be subtracted at each step, but the above circuit can only subtract two. The solution is to connect two copies of it: a first copy subtracts  $b_i$  from  $a_i$ , and a second subtracts  $c_{i-1}$  from the result of the first. Each copy produces a new carry, but at most one of these can be 1. Indeed, if  $a_i - b_i$  gives a carry then the second stage necessarily subtracts  $c_{i-1}$  from 1, which cannot give a carry. Hence the new carry  $c_i$  resulting from  $a_i - b_i - c_{i-1}$  can be computed with a disjunction of the carries from the two half-subtractors. This leads to the *full subtractor* circuit shown in Figure 2.9.

Finally, to subtract two binary numbers with n bits each, we simply need to connect n full subtractor circuits, with the output carry  $c_i$  of step i connected to the input carry  $c_{i-1}$  of step i + 1 (see Figure 2.9).

### 2.4.3 Arithmetic and Logic Unit

As shown in Section 1.2.1, multiplying two binary numbers a and b boils down to additions of left shifted copies of a, each multiplied by a bit of b. Furthermore,  $a_i * b_j$  gives the same result as  $a_i \wedge b_j$ . Hence a circuit to multiply two n-bit binary numbers (yielding 2n bits) can be obtained with n copies of an n-bit adder, plus  $n^2$  AND gates to compute the  $a_i \wedge b_j$  terms.

Comparing two *n*-bit binary numbers is also easy to do. Indeed:

- a = b if and only if the *n* least significant bits of a b are equal to 0.

- a > b if and only if at least one of the *n* least significant bits of a b is different from 0, and if there is no carry in the  $n^{th}$  column (counting from 0).

- a < b if and only if at least one of the *n* least significant bits of a b is different from 0, and if there *is* a carry in the  $n^{th}$  column (counting from 0).

Hence a subtractor circuit, plus a another computing whether its output (excluding the carry) is different from 0, is sufficient to compare two numbers.

Finally, circuits computing bitwise logical operations on n-bit numbers are trivial to implement. Indeed, we just need n copies of the corresponding logic gate, each computing one bit of the result, independently of the others (*i.e.*, in parallel).

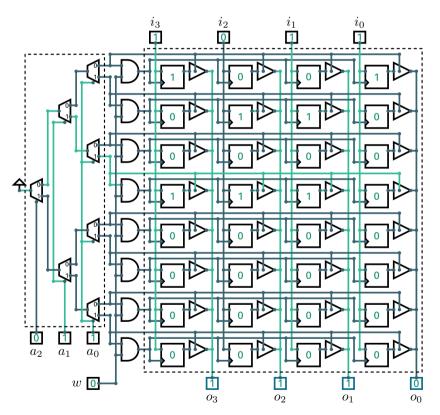

All these circuits can be put together into a larger circuit called an *Arithmetic and Logic Unit*. Such a circuit accepts two binary numbers as input, plus a third one specifying an operation to perform on them. It produces as output the result of this operation, on the given numbers.

For instance, a very simple Arithmetic "and Logic" Unit which can only perform additions, subtractions, and comparisons is shown in Figure 2.10. If its subtract input is 1 it subtracts its two 4-bit inputs. Otherwise it adds them. For this it uses a subtractor circuit where the NOT gates are replaced with XOR gates, connected to the subtract input. When this input is 0, the XOR gates behave as a simple wire  $(p \oplus 0 = p)$ , which gives an adder circuit. When subtract is 1 these gates behave as NOT gates  $(p \oplus 1 = \neg p)$ , yielding a subtractor. Finally, three OR gates compute whether at least one bit of the output is 1. Together with the carry bit, this can be used to compare the inputs, as explained above.

To conclude this chapter, it should be noted that a relay takes some time to switch between its active and inactive states (because its moving metallic piece cannot move instantly). This is the case for transistors too. Consequently, the output of a logic gate does not change instantly when its inputs change. And this is the same for all circuits. The more logic gates there is between an input and an output, the longer it takes for an input change to *propagate* to the output. These propagation delays must be taken into account in some circuits, including some presented in the next chapters.

**CHAPTER**

The very basic Arithmetic Unit presented in the previous chapter can perform several operations, but only one at a time. To do a sequence of operations one has to memorize intermediate results, or to note them somewhere. For instance, to add a, b, and c, one has to set the inputs to a and b, memorize the output a + b, and replace the inputs with a + b and c (changing the inputs immediately changes the output, hence one cannot directly "copy" it to an input). To avoid this mental or manual work, a solution is to use additional circuits to memorize intermediate results. This chapter explains how this can be done with logic gates.

### 3.1 Memory cells

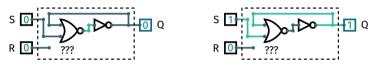

### 3.1.1 SR latch

A circuit which can memorize a single bit must have some inputs to set the value to memorize, and an output equal to the last memorized value, noted Q. One possibility is to use one input to *set* the memorized value to 1, noted S, and another to *reset* it to 0, noted R. Connecting S to the power source should change Q to 1, but connecting it to the ground should *not* change Q to 0 (otherwise this circuit would have no "memory"). Likewise, setting R to 1 should reset Q to 0, but setting it to 0 should not change Q. In particular, when both S and R are 0, Q should keep its memorized value, which can be 0 or 1.

The above requirements lead to a circuit whose output is not completely determined by its current inputs, unlike all the circuits presented so far (since Q can be 0 or 1 when S = R = 0). To achieve this a solution is to use a "hidden" input equal to the last value of Q, noted  $Q_{\text{last}}$ . Then Q can be defined as a function of its inputs again ( $Q = Q_{\text{last}}$  if S = R = 0). By definition  $Q_{\text{last}}$  is the last output of the circuit, which leads to a loop:

When S = R = 0, Q should be equal to the  $Q_{\text{last}}$  input. For this the circuit in the above box cannot simply connect Q to  $Q_{\text{last}}$ , since an electric current cannot flow in a

#### **CHAPTER 3** Register and Memory Circuits

loop. A solution is to use two NOT gates in series instead. Indeed, this leads to a loop which has two stable states, Q = 0 and Q = 1:

To set Q to 1 we need to force the output of the right NOT gate to 1 or, equivalently, to force the output of the left NOT gate to 0. The latter can be done by replacing the left NOT gate with a NOR gate connected to S:

Indeed, this NOR gate behaves like a NOT gate when S = 0 (since  $\neg(x \lor 0) = \neg x$ ), but forces its output to 0 when S = 1 (because  $\neg(x \lor 1) = 0$ ). Similarly, we can set Q to 0 when R = 1 by replacing the remaining NOT gate with a NOR gate connected to R. This yields the following circuit, called an *SR latch*:

If S = R = 1 the two NOR gates force their output to 0. Switching from this state to S = R = 0 make them behave as NOT gates again, but starting with their input and output equal to 0. This state is unstable: depending on which gate updates its output to 1 first, the end result can be Q = 0 or Q = 1 (or, in theory, an infinite oscillation between 0 and 1). For this reason S and R must not be set to 1 at the same time. Note that the above unstable state also occurs when the circuit is powered on. In the following we assume that the R input of each SR latch is briefly set to 1 when circuits are powered on, so that their initial state is always 0.

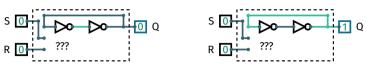

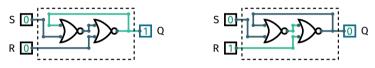

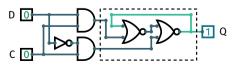

### 3.1.2 D latch

Using set and reset inputs is only one possibility to change the memorized value Q. Another is to set Q to the current value of some "data" input, noted D, when a "copy" input, noted C, is 1 (and to keep it unchanged when C = 0). In other words, Q should be set to 1 when D = 1 and C = 1, should be reset to 0 when D = 0 and C = 1, and should keep its value when C = 0. This is easy to do with an SR latch and 3 more gates to convert D and C to appropriate values of S and R:

This circuit is called a *D* latch. One advantage, compared to the SR latch, is that it does not have forbidden inputs such as S = R = 1. Indeed, thanks to the gates in front of the SR latch, this case can never happen.

# 3.1.3 D flip-flop

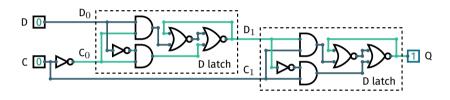

As long as C = 1, the output Q of a D latch changes each time D changes. This is not practical to memorize the value of D at a precise moment, unless C remains equal to 1 only for a very brief time (but long enough to allow the SR latch to stabilize to a potentially new state). To solve this issue, a possibility is to make sure that D does not change while C = 1. This can be done with two D latches in series, using opposite values for C, as shown below:

Indeed:

- when C = 1 the output  $D_1$  of the first D latch does not change when D changes, because  $C_0 = 0$ . Hence the output of the second D latch does not change either, although its  $C_1$  input is 1. In other words, the first D latch makes sure that  $D_1$  does not change while  $C_1 = 1$ , as required.

- when C = 0 the output  $D_1$  of the first D latch changes each time D changes, because  $C_0 = 1$ . But then  $C_1 = 0$  and thus the output Q of the second D latch does not change.

- when C changes from 1 to 0, the first D latch memorizes the value of D and its output D<sub>1</sub> changes to this potentially new value. But this takes some time, whereas C<sub>1</sub> changes immediately when C changes. Hence, when D<sub>1</sub> changes, C<sub>1</sub> is already 0, and thus Q does not change.

- when C changes from 0 to 1, the first D latch keeps its state, *i.e.*, D<sub>1</sub> remains equal to the current value of D (this was the case since C was last set to 0). But C<sub>1</sub> also changes from 0 to 1. The second D latch thus memorizes D, and Q changes to D.

In summary, this circuit<sup>1</sup>, called a D flip-flop, memorizes the value of D at the precise moment when C changes from 0 to 1, and keeps its state otherwise. In the following, to simplify figures and to make it easier to distinguish memory cells, we represent SR latches and D flip-flops as shown in Figure 3.1.

<sup>&</sup>lt;sup>1</sup>Other circuits can achieve the same effect, with less gates and transistors (especially with relays [5]).

### **CHAPTER 3** Register and Memory Circuits

**FIGURE 3.1** SR latches and D flip-flops are represented with their currently memorized value inside a large black square. The D flip-flop symbol differs from the SR latch symbol with a small black triangle on its *C* input.

# 3.2 Memory circuits

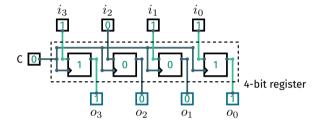

To memorize an intermediate result of the Arithmetic Unit we need to memorize n bits simultaneously. This is easy to do with n flip-flops connected to the same C input:

This circuit is called a *register*. It memorizes its input when C changes from 0 to 1. Its output is the last memorized value.

To memorize several intermediate results we can connect the n outputs of the Arithmetic Unit to several n bit registers. We can then choose in which register to store this output by activating the C input of only one of these registers. For instance, the following circuit can store a 4-bit number in one of 3 registers:

However, getting the value from one these registers is not very easy because this circuit has too many output wires. To make it easier to use we can add one more input

**FIGURE 3.2** The four possible input combinations of a tristate buffer and the corresponding outputs (left). A tristate buffer is like a normally open relay (right).

per register, to optionally connect its outputs to n shared output wires. For this we can connect the  $i^{th}$  flip flop of each register to a shared output wire  $o_i$  via a normally open relay:

Together with additional inputs  $G_j$ , connected to the control inputs of all the relays of the  $j^{th}$  register, this allows connecting or disconnecting a whole register to the shared output wires. Normally open relays used in this way are called *tristate buffers* and are represented as shown in Figure 3.2. Their name comes from the fact that their output can have 3 states: 0, 1, or "disconnected".

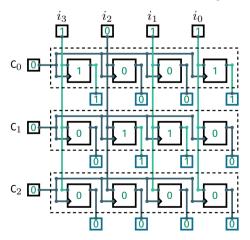

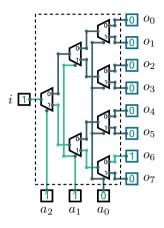

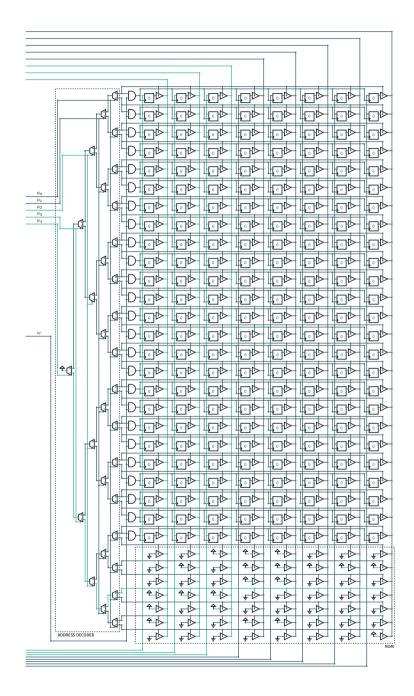

In the above circuit  $G_0$  and  $G_1$  must not be simultaneously set to 1. Indeed, doing so could connect together the outputs of two flip flops with different states, resulting in a short circuit. More generally, with more than 2 registers, at most one  $G_j$  input must be set to 1 at a time. This can be done with a *binary decoder*. A binary decoder with k inputs  $a_0, a_1, \ldots a_{k-1}$  has  $2^k$  outputs  $o_0, o_1, \ldots o_{2^k-1}$ . It sets its output  $o_j$  to its *i* input, and all the others to 0, where *j* is the binary number  $a_{k-1} \ldots a_1 a_0$ . This circuit can be implemented with several demultiplexers, as illustrated in Figure 3.3.

We can connect it to  $2^k$  registers as shown in Figure 3.4. This new circuit connects the outputs of the binary decoder to the  $G_j$  inputs of the registers and, via AND gates connected to a new w input, to their  $C_j$  inputs. This forms a *Random Access Memory* (RAM), called this way because it allows *reading* and *writing* (*i.e.*, to get and set) values in any order. For instance, with the circuit in Figure 3.4:

• reading the value of the  $j^{th}$  register can be done by setting the  $a_2a_1a_0$  inputs to the bits of j in binary. The value is then obtained on the  $o_3o_2o_1o_0$  outputs.  $j = a_2a_1a_0$  is called the *address* of this register.

# **CHAPTER 3** Register and Memory Circuits

**FIGURE 3.3** A binary decoder with 3 inputs. Here  $a_2a_1a_0 = 110_2 = 6$ , hence  $o_6 = i$ .

**FIGURE 3.4** A Random Access Memory (RAM) storing eight 4-bit values. This circuit currently reads the value at address  $a_2a_1a_0 = 011_2 = 3$ , namely  $1110_2$ . Setting w to 1 would write the input value  $i_3i_2i_1i_0 = 1011_2$  at address 3.

• writing a value v in the  $j^{th}$  register can be done by setting  $i_3i_2i_1i_0$  to the bits of v in binary, by setting the  $a_2a_1a_0$  inputs to the bits of j in binary, and finally by changing w from 0 to 1. The last step changes the C inputs of all the flip flops of the  $j^{th}$  register, making it memorize the shared inputs  $i_3i_2i_1i_0$ .

This basic circuit uses one address per group of 4 bits. In practice, most computers use one address per group of 8 bits, called a *byte*. They also use much more than 3 bits per address. A 10-bit address can refer to  $2^{10} = 1024$  bytes, called a *kilobyte* (KB). A 20-bit address can refer to 1024 kilobytes, called a *megabyte* (MB). And a 30-bit address can refer to one *gigabyte* (GB – 1024 megabytes).

# **3.3 Bus**

The above RAM circuit can store several intermediate results, but it has only one input address and one output value. Hence it is not sufficient, for instance, to directly add or subtract two intermediate results with the Arithmetic Unit. To solve this we can use two separate registers as input of the Arithmetic Unit, provided we have a way to copy values from the RAM to one or the other of these registers.

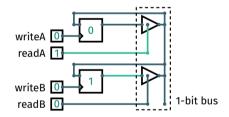

A circuit which can copy values from one register to another, or from a register to RAM or vice-versa, is called a *bus*. A 1-bit bus connecting n flip-flops is easy to build. We just need to connect the D input of each flip flop to a common wire, and to connect their Q output to this same wire via a tristate buffer, as in the RAM circuit:

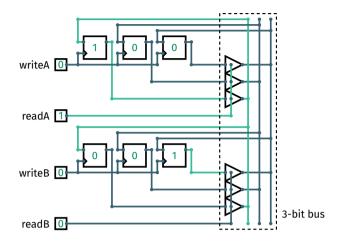

The above circuit can copy the value from A to B by setting readA to 1 and then by changing writeB from 0 to 1. The first step connects A's output to the bus and thus to the D input of B. The second step memorizes this value in B. Conversely, this circuit can copy the value from B to A by setting readB to 1 and then by changing writeA from 0 to 1. It easy to generalize to 3 or more flip-flops. It can also be generalized to an *n*-bit bus, to copy values between 2 or more *n*-bit registers, or the RAM. For instance, the circuit in Figure 3.5 can copy values between two 3-bit registers. It is made of three copies of the 1-bit bus, with shared "read" and "write" inputs. Copying 3-bit values from A to B or vice versa can be done as with the 1-bit bus.

To maintain a register connected in "read mode" to the bus we can memorize the "read" inputs in SR latches. And, to make it easier to read another register, we can connect the S input of each latch to the R input of all the others (so that setting one resets the others – as in the RAM, at most one register must be connected to the bus at a time). For instance, the circuit in Figure 3.6 sets readA to 1, readB to 0, and

## CHAPTER 3 Register and Memory Circuits

FIGURE 3.5 A 3-bit bus (right) connected to two 3-bit registers (left).

readC to 0 when selectA is 1, and keeps them in this state even if selectA is reset to 0. Similarly, it sets readB (resp. readC) to 1, and resets the others to 0, when selectB (resp. selectC) is 1. At most one "select" input must be set to 1 at a time.

# 3.4 Example

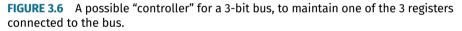

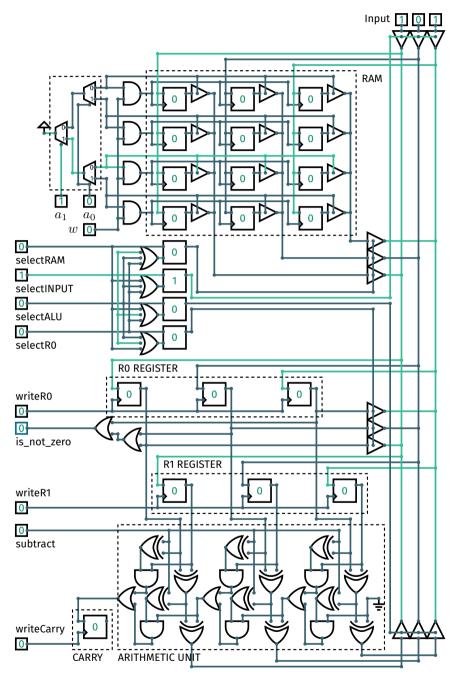

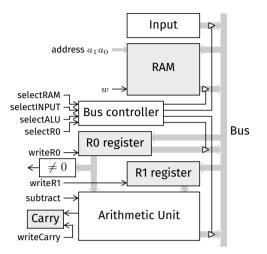

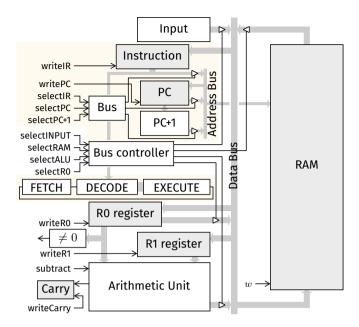

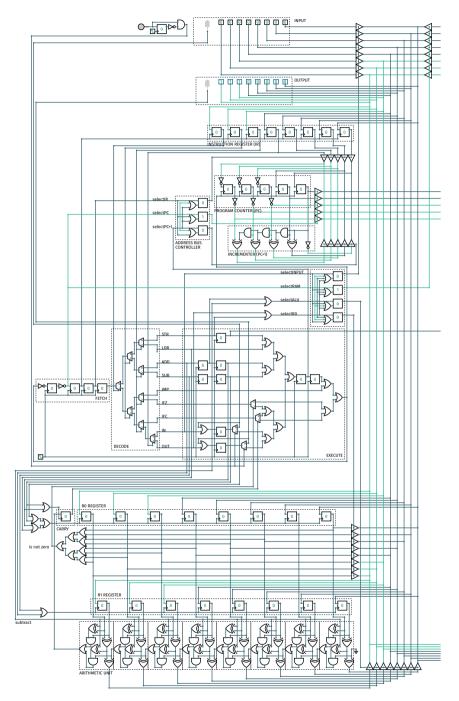

We can now use the circuits presented in this chapter to memorize the intermediate results of an Arithmetic and Logic Unit (ALU). The circuit in Figure 3.7 connects the ALU from Figure 2.10 (with 3 bits only to simplify) to 3 input bits, a RAM, and two registers named R0 and R1, via a bus, as schematized in Figure 3.8.

Thanks to the bus, this circuit can copy values from any source (Input, RAM, R0, or the ALU's output) to any sink (RAM, R0, or R1), which gives 4 \* 3 = 12 possibilities. For example, computing a + b - c can be done as follows:

• set the input to *a* and copy it in R0. For this, first send a *pulse* on selectINPUT (*i.e.*, set it to 1 for a short time and then reset it to 0). Then send a pulse on writeR0 (this memorizes *a* when writeR0 changes from 0 to 1).

### 3.4 Example

**FIGURE 3.7** A 3-bit Arithmetic Unit (bottom) connected to 3 input bits (top right), a 4 values RAM (top left), and 2 registers R0 and R1 (middle), via a bus (right).

#### CHAPTER 3 Register and Memory Circuits

FIGURE 3.8 The block diagram corresponding to Figure 3.7.

- set the input to b and copy it in R1 by sending a pulse on writeR1 (there is no need to send a pulse on selectINPUT first since the bus controller keeps the last selected source connected).

- set and maintain "subtract" to 0, send a pulse on selectALU, and wait a short time until the ALU has computed a + b. Then store the result in R0 by sending a pulse on writeR0.

- set the input to c and copy it in R1 by sending a pulse on selectINPUT, followed by a pulse on writeR1.

- set and maintain "subtract" to 1, send a pulse on selectALU, and wait a short time until the ALU has computed a + b (in R0) minus c (in R1). Then store the result in R0 by sending a pulse on writeR0.

At this stage we can use the is\_not\_zero and carry outputs, for instance, to test if a + b - c is equal to 0, or to compare a + b and c. We can also store a + b - c in RAM for later use. For this it suffice to send a pulse on selectR0, followed by a pulse on w, after having set  $a_1a_0$  to the desired destination address.

CHAPTER

Control Circuits

Thanks to registers and memory circuits we can use an Arithmetic and Logic Unit to perform computations without having to mentally memorize intermediate results. Instead, as shown in the previous chapter, we can simply send a series of pulse signals on the correct inputs, and in the correct order. But this requires to memorize this procedure. And executing it manually is very slow and error-prone, even if the circuit does each operation very quickly. To solve the first issue a solution is to store some description of the desired procedure in Random Access Memory. To solve the second one we can use new circuits to execute this procedure for us, by sending the appropriate pulses. This chapter explains how this can be done.

# 4.1 Instructions

A procedure such as the one presented in Section 3.4 could be described in an abstract way as "read 3 numbers a, b, and c in input, compute a + b - c, and write the result in RAM at address x". However, representing such descriptions with one or more numbers which can be stored in RAM is not easy. And figuring out which pulses to send to execute them would also be quite complicated.

This procedure can also be described as a sequence of elementary actions: "wait an input value", "send a pulse on selectInput", "send a pulse on writeR0", "wait an input value", "send a pulse on writeR1", etc. Each action can easily be represented with a small number (*e.g.*, 0 for "wait an input value", 1 for "send a pulse on selectInput", etc.). And each action is easy to execute. However, such a description is hard to design and to understand for humans (because its high level meaning is lost in the details).

A trade-off is to describe this procedure with more abstract actions, but not too abstract either, called *instructions*. For instance, an instruction could be "wait an input value and store it in R0", "add the values in R0 and R1 and store the result in R0", or "copy the value in R0 in RAM, at address 3". As shown below, such instructions are not too complex to represent with a number, called their *encoding* (to store them in memory). And they are still quite simple to execute (each instruction only requires sending 2 or 3 pulses at most). Finally, a sequence of instructions is less hard to design and to understand than the corresponding sequence of pulses (but still quite hard; we address this problem in Part 3).

Simple procedures, also called *programs*, can be described with a sequence of

#### CHAPTER 4 Control Circuits

instructions, to be executed one after the other. For this we can store their encoding one after the other in memory, *i.e.*, at consecutive addresses. Then, after the instruction at address a is executed, the one at address a + 1 should execute<sup>1</sup>.

# 4.1.1 Jump instructions

Some programs need to repeat the same sequence of instructions two or more times. For instance, a "calculator" program needs to repeat forever the same sequence (read two numbers in input, compute and output their sum, repeat). In other words, after the last instruction of the sequence is executed, the instruction at the next address should *not* be executed. Instead, execution should restart at the first instruction of the sequence. This can be described with a so called *jump instruction*. A "jump to a" instruction specifies that the next instruction to execute is the one at address *a*.

In many cases a sequence of instructions must be repeated a precise number of times. For instance, to compute a \* b with the circuit of Figure 3.7, we can repeat b times a sequence adding a to R0 (initially set to 0). Then, after a has been added to R0, there are two cases: either we need to repeat the sequence again, or we need to continue with the rest of the program (*e.g.*, output the result a \* b). This can be described with a *conditional jump* instruction. Such an instruction either jumps to a given address, or continues to the instruction at the next address, depending on some condition (for instance, whether R0 is equal to 0 or not).

# 4.2 A toy instruction set

To illustrate the above discussion we define in this section a concrete set of instructions for a circuit such as the one in Figure 3.7 (*i.e.*, with a RAM and two registers R0 and R1 as input of a very basic Arithmetic Unit). These instructions are the following:

- Memory:

- the Load instruction copies the value at a given address a into the R0 register.

- the Store instruction copies the value in the R0 register at a given address a.

- Arithmetic:

- the Add instruction adds the value at address *a* to the value in the R0 register, and stores the result in R0.

- the Subtract instruction subtracts the value at address *a* from the value in the R0 register, and stores the result in R0.

- Jumps:

- the Jump instruction specifies that the next instruction to execute is the one at address *a*.

<sup>&</sup>lt;sup>1</sup>Assuming that each encoded instruction can fit in the n bits between two consecutive addresses.

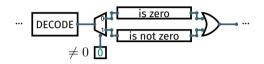

- the Jump If Zero instruction specifies that the next instruction to execute is the one at address *a* if the value in R0 is equal to 0. Otherwise execution continues with the instruction at the next address.

- the Jump If Carry instruction specifies that the next instruction to execute is the one at address *a* if the last Add or Subtract instruction produced a non-zero carry bit. Otherwise execution continues with the instruction at the next address.

- Input and output:

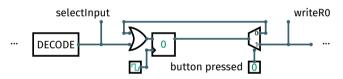

- the Input instruction waits for the user to press a button, and then copies the value on the input wires into the R0 register.

- the Output instruction displays the value in the R0 register, and then waits until the user presses a button.

# 4.2.1 Encoding

The above *instruction set* contains 9 instructions. We can thus give them numbers from 0 to 8, called *operation codes*, or *opcodes*. This requires at least 4 bits to encode each instruction. But all instructions except the last two have an associated address *a*, called an *operand*. This operand must also be encoded as part of the instruction, which requires more bits.

In the following we assume that the memory contains  $2^5 = 32$  bytes, each with their own address, and that R0, R1, and the Arithmetic Unit work on 8-bit values. We then use 5 bits per address, and we encode each instruction in one byte, as follows:

| LDR | $\mathrm{R0} \leftarrow \mathrm{mem8}[a]$               |         |

|-----|---------------------------------------------------------|---------|

| STR | $\mathrm{R0} \to \mathrm{mem8}[a]$                      |         |

| ADD | $\mathbf{R0} \leftarrow \mathbf{R0} + \mathbf{mem8}[a]$ |         |

| SUB | $R0 \leftarrow R0 - mem8[a]$                            | 0 1 1 a |

| JMP | jump to a                                               |         |

| IFZ | if $R0 = 0$ then jump to $a$                            |         |

| IFC | if carry $\neq 0$ then jump to $a$                      |         |

| IN  | $R0 \leftarrow input$                                   | 1 1 1 0 |

| OUT | $R0 \rightarrow output$                                 | 1 1 1 1 |

The left column is the *instruction mnemonic*, an abbreviation of the instruction name. The middle column is a symbolic description of the effect each instruction. Here  $dst \leftarrow src$  or  $src \rightarrow dst$  means a copy of the value in src into dst, and mem8[a] means the 8-bit value at address a. Finally, the right column is the binary number corresponding to this instruction, *i.e.*, its encoding. For instance, the encoding of the LDR 7 instruction, which copies the byte at address  $7 = 111_2$  into R0, is  $001_2$  followed by 7 encoded in 5 bits,  $00111_2$ , which gives  $00100111_2 = 39$ .

#### **CHAPTER 4** Control Circuits

### 4.2.2 Example program

With the above instruction set a "calculator" program adding numbers in an endless loop can be implemented as follows:

| IN     | $R0 \leftarrow input$                                                | 1 1 1 0 0 0 0 0                     | 0 |

|--------|----------------------------------------------------------------------|-------------------------------------|---|

| STR    | $R0 \rightarrow mem8[6]$                                             | $0_0_0_0_0_1_1_0$                   | 1 |

| IN     | $R0 \leftarrow input$                                                | 1 1 1 0 0 0 0 0                     | 2 |

| ADD    | $\mathbf{R0} \leftarrow \mathbf{R0} + \mathbf{mem8}[\boldsymbol{6}]$ | 0 1 0 0 0 1 1 0                     | 3 |